Home > Support > Datasheets > U6 Datasheet > 2 - Hardware Description > 2.8 - Digital I/O

### 2.8 - Digital I/O [U6 Datasheet]

Log in or register to post comments

### Digital I/O Overview

The LabJack U6 has 20 digital I/O. The LabJackUD driver uses the following bit numbers to specify all the digital lines:

0-7 FIO0-FIO7 8-15 EIO0-EIO7 16-19 CIO0-CIO3 20-22 MIO0-MIO2

Note: On the U6/U6-Pro the digital lines CIO0-2 and MIO0-2 are shared. This means that changing the state of MIO0-2 will also change the state of CIO0-2. Therefore, anyone using two accessory boards with a U6 needs to be aware that they can use either CIO0-2 or MIO0-2, but cannot use both simultaneously. MIO0-2 are used to control extended analog channels, so if you are reading extended channels from the Mux80 you do not want to use slots 8-10 on the RB12 (only use slots 0-7 & 11).

The "F", "E", "C", and "M" designators have little special meaning. They are just arbitrary letters used to designate different groupings of digital I/O. The generic designator DIOx is sometimes used to specify any digital I/O from 0 to 22, so for example an alternative name for EIO0 is DIO8.

The U6 has 8 FIO. The first 4 lines, FIO0-FIO3, appear both on the screw terminals and on the DB37 connector. The upper 4 lines appear only on the DB37 connector. By default, the FIO lines are digital I/O, but they can also be configured as up to 4 timers and 2 counters (see Timers/Counters Section of this User's Guide).

The 8 EIO and 4 CIO lines appear only on the DB15 connector. See the DB15 Section of this User's Guide for more information.

Up to 6 of the FIO/EIO lines can be configured as timers and counters. These are enabled sequential starting from FIO0-EIO0 (determined by pin offset). Thus, any sequential block of 1-6 digital I/O, starting from FIO0 to EIO0, can be configured as up to 4 timers and up to 2 counters.

MIO are standard digital I/O that also have a special multiplexer control function described in <u>Section 2.6</u> above (AIN). The MIO are addressed as digital I/O bits 20-22 by the Windows driver.

The MIO hardware (electrical specifications) is the same as the EIO/CIO hardware.

#### **Max Current & Overvoltage Protection**

All the digital I/O include an internal series resistor that provides overvoltage/short-circuit protection. These series resistors also limit the ability of these lines to sink or source current. Refer to the specifications in <u>Appendix A</u>.

#### Tri-State I/O

All digital I/O on the U6 have 3 possible states: input, output-high, or output-low. Each bit of I/O can be configured individually. When configured as an input, a bit has a  $\sim 100 \text{ k}\Omega$  pull-up resistor to 3.3 volts (all digital I/O are 5 volt tolerant). When configured as output-high, a bit is connected to the internal 3.3 volt supply (through a series resistor). When configured as output-low, a bit is connected to GND (through a series resistor).

When only lightly loaded, an input terminal will measure about 3.3 volts if measured with a DMM, and thus it can be tough to use a DMM to tell whether a line is set to input or output-high. A couple tips to tell the difference:

- 1. Look for a slight change where output-high measures a little higher. For example, a DMM might show 3.300 for input and 3.315 for output-high.

- 2. Add a load resistor. If you add a 100k from DIOx to GND, it should read about 1.6V for input and 3.3V for output-high.

#### **5 Volt Output**

The fact that the digital I/O are specified as 5-volt tolerant means that 5 volts can be connected to a digital input without problems (see the actual limits in the specifications in Appendix A). If 5 volts is needed from a digital output, consider the following solutions:

- Use the <u>LJTick-DigitalOut5V</u> to convert a pair of digital outputs to 5V logic.

- In some cases, an open-collector style output can be used to get a 5V signal. To get a low set the line to **output-low**, and to get a high set the line to**input** (... note that this does not work with timer outputs, e.g. PWM, as they toggle the line between output-low and output-high). When the line is set to input, the voltage on the line is determined by a pull-up resistor. The U3 has an internal ~100k resistor to 3.3V, but an external resistor can be added to a different voltage. Whether this will work depends on how much current the load is going to draw and what the required logic thresholds are. Say for example a 10k resistor is added from EIO0 to VS. EIO0 has an internal 100k pull-up to 3.3 volts and a series output resistance of about 180 ohms. Assume the load draws just a few microamps or less and

thus is negligible. When EIO0 is set to input, there will be 100k to 3.3 volts in parallel with 10k to 5 volts, and thus the line will sit at about 4.85 volts. When the line is set to output-low, there will be 180 ohms in series with the 10k, so the line will be pulled down to about 0.1 volts.

- A surefire way to get 5 volts from a digital output is to add a simple logic buffer IC that is powered by 5 volts and recognizes 3.3 volts as a high input. Consider the CD74ACT541E from TI (or the inverting CD74ACT540E). All that is needed is a few wires to bring VS, GND, and the signal from the LabJack to the chip. This chip can level shift up to eight 0/3.3 volt signals to 0/5 volt signals and provides high output drive current (+/-24 mA).

- Note that the 2 DAC channels on the U3 can be set to 5 volts, providing 2 output lines with such capability.

#### **Boot-Up Defaults**

The power-up condition of the digital I/O can be configured by the user with the "Config Defaults" option in LJControlPanel. From the factory, all digital I/O are configured to power-up as inputs. Note that even if the power-up default for a line is changed to output-high or output-low, there is a delay of about 5 ms at power-up where all digital I/O are in the factory default condition. For more information see this forum topic.

#### Why Are My Digital I/O "High" at Boot-Up?

The implied question here is "why do my DIO boot up as output-high from the factory". The answer is that per the "Boot-Up Defaults" section above the factory default state for all DIO is input, but since inputs have a 100k internal pull-up they will read 3.3 volts if only lightly loaded. So likely you are seeing that the state of your DIO is input, not output-high. Also see the "Tri-State I/O" section above.

#### Making An Input Read Low By Default

If you want a floating digital input to read low, an external pull-down resistor can be added to overpower the internal 100k pull-up. 4.7k to 22k would be a typical range for this pull-down, with 10k being a solid choice for most applications.

#### **Software Interface**

The low-level Feedback function (Section 5.2.5) writes and reads all digital I/O. For information about using digital I/O under the Windows LabJackUD driver, see Section 4.3.5. See Section 3.0 for timing information.

#### **Bit-Packed Integers**

Many function parameters contain specific bits within a single integer parameter to write/read specific information. In particular, most digital I/O parameters contain the information for each bit of I/O in one integer, where each bit of I/O corresponds to the same bit in the parameter (e.g. the direction of FIO0 is set in bit 0 of parameter FIODir). For instance, in the low-level function ConfigU3, the parameter FIODirection is a single byte (8 bits) that writes/reads the power-up direction of each of the 8 FIO lines:

- if FIODirection is 0, all FIO lines are input,

- if FIODirection is 1 (20), FIO0 is output, FIO1-FIO7 are input,

- if FIODirection is 5  $(2^0 + 2^2)$ , FIO0 and FIO2 are output, all other FIO lines are input,

- if FIODirection is 255 ( $2^0 + ... + 2^7$ ), FIO0-FIO7 are output.

#### **Duplicated Terminals (FIO0-FIO3)**

FIO0-FIO3 appear on the built-in screw-terminals and also on the DB37 connector. You should only connect to one or the other, not both at the same time.

To prevent damage due to accidental short circuit, both connection paths have their own series resistor. All FIO lines have a 470 ohm series resistor (that is included in the 550 ohm total impedance), and in the case of FIO0-FIO3 the duplicated connections each have their own series resistor, so if you measure the resistance between the duplicate terminals you will see about 940 ohms.

## 2.8.1 - Typical Digital I/O Connections [U6 Datasheet]

<u>Log in</u> or <u>register</u> to post comments

### 2.8.1.1 - Input: Driven Signals [U6 Datasheet]

Log in or register to post comments

The most basic connection to a U6 digital input is a driven signal, often called push-pull. With a push-pull signal the source is typically providing a high voltage for logic high and zero volts for logic low. This signal is generally connected directly to the U6 digital input, considering the

voltage specifications in Appendix A. If the signal is over 5 volts, it can still be connected with a series resistor. The digital inputs have protective devices that clamp the voltage at GND and VS, so the series resistor is used to limit the current through these protective devices. For instance, if a 24 volt signal is connected through a 22 k $\Omega$  series resistor, about 19 volts will be dropped across the resistor, resulting in a current of 0.9 mA, which is no problem for the U6. The series resistor should be 22 k $\Omega$  or less, to make sure the voltage on the I/O line when low is pulled below 0.8 volts.

The other possible consideration with the basic push-pull signal is the ground connection. If the signal is known to already have a common ground with the U6, then no additional ground connection is used. If the signal is known to not have a common ground with the U6, then the signal ground can simply be connected to U6 GND. If there is uncertainty about the relationship between signal ground and U6 ground (e.g. possible common ground through AC mains), then a ground connection with a 100  $\Omega$  series resistor is generally recommended (see Section 2.6.3.4).

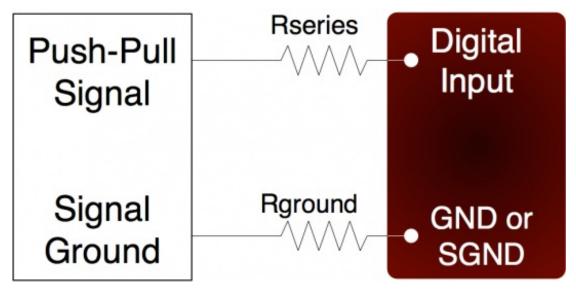

Figure 2.8.1.1-1. Driven Signal Connection To Digital Input

Figure 2.8.1.1-1 shows typical connections. Rground is typically 0-100  $\Omega$ . Rseries is typically 0  $\Omega$  (short-circuit) for 3.3/5 volt logic, or 22 k $\Omega$  (max) for high-voltage logic. Note that an individual ground connection is often not needed for every signal. Any signals powered by the same external supply, or otherwise referred to the same external ground, should share a single ground connection to the U6 if possible.

When dealing with a new sensor, a push-pull signal is often incorrectly assumed when in fact the sensor provides an open-collector signal as described next.

## 2.8.1.2 - Input: Open-Collector Signals [U6 Datasheet]

Log in or register to post comments

For details about open-collector, open-drain, NPN, or PNP connections, see the <u>Open-Collector Signals App</u> Note.

### 2.8.1.3 - Input: Mechanical Switch Closure [U6 Datasheet]

Log in or register to post comments

To detect whether a mechanical switch (dry contact) is open or closed, connect one side of the switch to U6 ground and the other side to a digital input. The behavior is very similar to the open-collector described above.

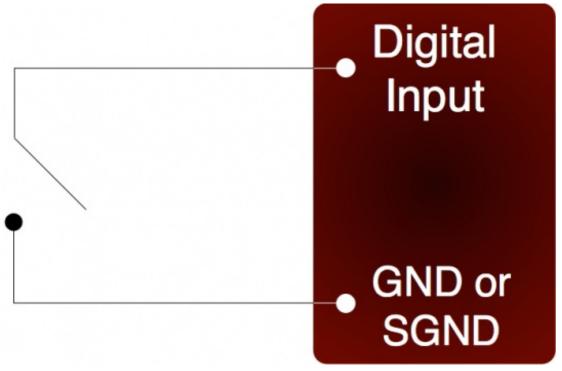

Figure 2.8.1.3-1. Basic Mechanical Switch Connection To Digital Input

When the switch is open, the internal 100 k $\Omega$  pull-up resistor will pull the digital input to about 3.3 volts (logic high). When the switch is closed, the ground connection will overpower the pull-up resistor and pull the digital input to 0 volts (logic low). Since the mechanical switch does not have any electrical connections, besides to the LabJack, it can safely be connected directly to GND,

without using a series resistor or SGND.

When the mechanical switch is closed (and even perhaps when opened), it will bounce briefly and produce multiple electrical edges rather than a single high/low transition. For many basic digital input applications, this is not a problem as the software can simply poll the input a few times in succession to make sure the measured state is the steady state and not a bounce. For applications using timers or counters, however, this usually is a problem. The hardware counters, for instance, are very fast and will increment on all the bounces. Some solutions to this issue are:

- Software Debounce: If it is known that a real closure cannot occur more than once per some interval, then software can be used to limit the number of counts to that rate.

- Firmware Debounce: See section 2.9.1 for information about timer mode 6.

- Active Hardware Debounce: Integrated circuits are available to debounce switch signals.

This is the most reliable hardware solution. See the MAX6816 (maxim-ic.com) or EDE2008 (elabinc.com).

- Passive Hardware Debounce: A combination of resistors and capacitors can be used to debounce a signal. This is not foolproof, but works fine in most applications

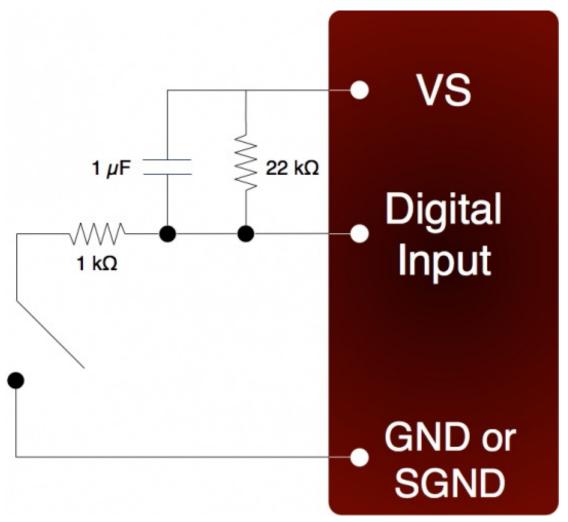

Figure 2.8.1.3-2. Passive Hardware Debounce

Figure 2.8.1.3-2 shows one possible configuration for passive hardware debounce. First, consider the case where the 1  $k\Omega$  resistor is replaced by a short circuit. When the switch closes it

immediately charges the capacitor and the digital input sees logic low, but when the switch opens the capacitor slowly discharges through the 22 k $\Omega$  resistor with a time constant of 22 ms. By the time the capacitor has discharged enough for the digital input to see logic high, the mechanical bouncing is done. The main purpose of the 1 k $\Omega$  resistor is to limit the current surge when the switch is closed. 1 k $\Omega$  limits the maximum current to about 5 mA, but better results might be obtained with smaller resistor values.

# 2.8.1.4 - Output: Controlling Relays [U6 Datasheet]

Log in or register to post comments

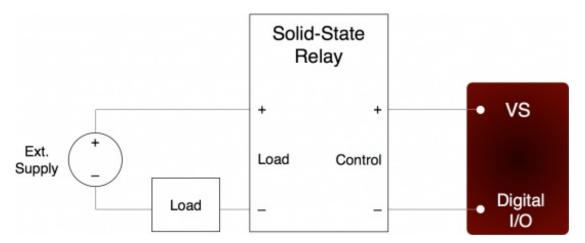

All the digital I/O lines have series resistance that restricts the amount of current they can sink or source, but solid-state relays (SSRs) can usually be controlled directly by the digital I/O. The SSR is connected as shown in the following diagram, where VS (~5 volts) connects to the positive control input and the digital I/O line connects to the negative control input (sinking configuration).

Figure 2.8.1.4-1. Relay Connections (Sinking Control, High-Side Load Switching)

When the digital line is set to output-low, control current flows and the relay turns on. When the digital line is set to input, control current does not flow and the relay turns off. When the digital line is set to output-high, some current flows, but whether the relay is on or off depends on the specifications of a particular relay. It is recommended to only use output-low and input.

For example, the Series 1 (D12/D24) or Series T (TD12/TD24) relays from Crydom specify a max turn-on of 3.0 volts, a min turn-off of 1.0 volts, and a nominal input impedance of 1500  $\Omega$ .

• When the digital line is set to output-low, it is the equivalent of a ground connection with 180  $\Omega$  (EIO/CIO/MIO) or 550  $\Omega$  (FIO) in series. When using an EIO/CIO/MIO line, the resulting voltage across the control inputs of the relay will be about 5\*1500/(1500+180) = 4.5 volts (the other 0.5 volts is dropped across the internal resistance of the EIO/CIO/MIO line). With an FIO line the voltage across the inputs of the relay will be about 5\*1500/(1500+550) = 3.7 volts (the other 1.3 volts are dropped across the internal resistance of the FIO line). Both of these are well above the 3.0 volt threshold for the relay, so it will turn on.

- When the digital line is set to input, it is the equivalent of a 3.3 volt connection with 100 k $\Omega$  in series. The resulting voltage across the control inputs of the relay will be close to zero, as virtually all of the 1.7 volt difference (between VS and 3.3) is dropped across the internal 100 k $\Omega$  resistance. This is well below the 1.0 volt threshold for the relay, so it will turn off.

- When the digital line is set to output-high, it is the equivalent of a 3.3 volt connection with 180  $\Omega$  (EIO/CIO/MIO) or 550  $\Omega$  (FIO) in series. When using an EIO/CIO/MIO line, the resulting voltage across the control inputs of the relay will be about 1.7\*1500/(1500+180) = 1.5 volts. With an FIO line the voltage across the inputs of the relay will be about 1.7\*1500/(1500+550) = 1.2 volts. Both of these in the 1.0-3.0 volt region that is not defined for these example relays, so the resulting state is unknown.

Mechanical relays require more control current than SSRs, and cannot be controlled directly by the digital I/O on the U6. To control higher currents with the digital I/O, some sort of buffer is used. Some options are a discrete transistor (e.g. 2N2222), a specific chip (e.g. ULN2003), or an op-amp.

Note that the U6 DACs can source enough current to control almost any SSR and even some mechanical relays, and thus can be a convenient way to control 1 or 2 relays.

The <u>RB12 relay board</u> is a useful accessory available from LabJack. This board connects to the DB15 connector on the U6 and accepts up to 12 industry standard I/O modules (designed for Opto22 G4 modules and similar).

Another accessory available from LabJack is the <u>LJTick-RelayDriver</u>. This is a two channel module that plugs into the U6 screw-terminals, and allows two digital lines to each hold off up to 50 volts and sink up to 200 mA. This allows control of virtually any solid-state or mechanical relay.